Our research focuses on intelligent VLSI circuits and systems, artificial intelligence (AI) hardware, hardware design for privacy, and AI for biomedical applications. our group is interested in exploring device, circuit, architecture, and application-level solutions for developing efficient computing circuits and systems, with an emphasis on AI, videos, and cancer detection.

Artificial intelligence (AI) hardware (Project Website)

|

RII Track 2 FEC: Building Research Infrastructure and Workforce in Edge Artificial Intelligence

NSF OIA-2218046: Role: PI, Period: 08/2022-07/2026, Sponsor: National Science Foundation. |

|

IRES Track I: Collaborative Research: Application-Specific Asynchronous Deep Learning IC Design for Ultra-Low Power

NSF OISE-1951488: Role: PI, Period: 09/2020-08/2024, Sponsor: National Science Foundation. |

Artificial Intelligence (AI), driven by deep neural networks (DNNs), has made spectacular advances in the past decade. Ongoing AI success is enabled by the computers such as large-scale clusters and servers and availability of big sets of data collected by Internet of Things (IoT) edge devices. However, the current cloud-based infrastructure associated with AI leads to response latency, excessive dependence on internet connectivity, and privacy concerns. Thus, there is a desire to push AI frontiers to edge devices to support AI locally, i.e. Edge AI. Edge AI, currently in its early stages, has several challenges. First, Edge AI “has a hardware problem”. Edge devices are typically powered by batteries, thereby having very stringent limitations in energy consumption, computational capability, memory storage, footprint, and cost. Under these constraints, low-cost and ultra-low power deep learning hardware is in critical need. As compared to general-purpose hardware platforms (e.g., CPU, GPU, or field-programmable gate arrays (FPGAs)), Application-Specific Integrated Circuits (ASICs) are superior to support Edge AI in performance, volume, and power consumption. Supported by the NSF grant OISE-1951488, my team developed a context-aware power-efficient and low-cost memory design technique for deep learning systems. We conducted an off-line data-mining-assisted, synaptic data correlation and association relationship study and subsequently designed a context-aware memory that can store synaptic weights efficiently with data self-recovery capability in the presence of memory failures. In addition to the hardware challenge, Edge AI has several other challenges: AI algorithms such as DNNs have huge computational requirements, which cannot be supported by resource-constrained edge devices. Also, the availability and usability of data on edge is another key to Edge AI, which requires advanced sensors. Last, but not least, an effective solution is critical to integrate the hardware, software, and data into an edge device that meets the requirement of a specific AI use case. In order to address such challenges and needs, supported by another NSF grant OIA-2218046, as principal investigator (PI), I am collaborating with 15 professors from six universities from Alabama, Arkansas, and North Dakota to develop a research infrastructure for Edge AI with novel algorithms, hardware, sensing technologies, and devices. In this project, my team is leading the development of an Edge AI device platform by exploiting novel AI ASIC and nano-sensors to meet the requirements of different use cases, including diabetes management, cancer detection, and video processing. Read More on Project Website

Hardware Design for Privacy

|

Collaborative Research: CNS Core: Small: Privacy by Memory Design

NSF CNS-2211215: Role: PI, Period: 08/2022-12/2025, Sponsor: National Science Foundation. |

With the advent of cyber technologies, the collection, sharing, and analysis of individual’s data becomes much faster and more ubiquitous. Despite the increased convenience, the concern for data privacy is immense. Among existing privacy-enhancing techniques, differential privacy (DP) has been widely accepted as the de facto standard for preserving data privacy. Although the decade-long research efforts on DP has almost stretched its mathematical rigor, notion completeness, algorithm optimality, and domain applicability to the full extent, there still exists a critical research problem that has been largely overlooked — the software-based realization of DP mechanisms. Specifically, all existing DP studies are grounded on the hypothesis that software can easily and faithfully add a secret number (i.e., DP noise) sampled from a probability distribution (i.e., a designed DP mechanism) to the true value. However, the rigor and practicality of this hypothesis are challenged by recent empirical findings about its privacy violation and by the growing demand to implement DP in low-end devices that lack DP-related high-level code libraries. This project’s innovative research angle is to realize DP mechanisms directly on memories, which are ubiquitous in modern electronic devices. This ambition is motivated by a unique memory characteristic that the stored data are corrupted (i.e., randomized) when the memory operates at sub-nominal supply voltages. Supported by the NSF grant CNS-2211215, my team has developed a memory prototype to demonstrate the realization of local DP (LDP) on Static random-access memory (SRAM) and the achievement of significant power savings on memory read/write processes, in collaboration with Dr. Jianqing Liu of Computer Science at North Carolina State University. We designed a new memory architecture with a hybrid 6T-8T cell structure that achieves heterogeneous cell failures when operating at sub-nominal supply voltages. With such design, when data is read out from the memory, some bit positions can be controlled to flip their bit values (with the assistance of a peripheral circuitry for random number generation) while others can have their bit values remain unaltered. The cell failures (or bit flipping) are properly controlled via runtime power control to realize the randomized response (RR) on some specific binary bits of the stored data, thereby ensuring LDP on the original data. In the meantime, we purposefully rendered cell failures to the least significant bits (LSBs) to minimize the utility loss. When operating at a sub-nominal voltage, for instance at 500mV, the proposed memory realizes the local DP with ε value as 1.49 and it simultaneously enables 88.58% power savings as compared to the traditional memory.

Intelligent Efficient VLSI Circuits and Systems

|

SHF: Small: Turning Visual Noise into Hardware Efficiency: Viewer-Aware Energy-Quality Adaptive Mobile Video Storage

NSF CCF-1855706: Role: PI, Period: 10/2018-9/2022, Sponsor: National Science Foundation. |

|

EAGER: Data-Mining Driven Intelligent Power Efficient Memory Design for Mobile Video Applications

NSF CCF-1514780: Role: PI, Period: 10/2015-06/2018, Sponsor: National Science Foundation. |

Energy efficiency is a well-known principal design goal across all layers of computing systems (e.g., sensors, mobile, cloud). With diminishing benefits from CMOS technology scaling and increasing demands from unprecedented data size, new hardware innovation is greatly needed to enhance energy efficiency of computing systems. In the past 10+ years, with my students and collaborators, I have worked extensively on multi-level (device/circuit/architecture/application) solutions for developing intelligent efficient VLSI circuits and systems. Target applications encompass Internet-of-Things (IoT), mobile computing, high-performance computing with multi-core microprocessors, and application-driven design. During our design process, different performance parameters such as speed, reliability, cost, have been considered to meet the requirement of a variety of applications. As an example, I have been working on intelligent storage system for energy-efficient mobile videos, supported by two NSF grants (CCF-1855706 and CCF-1514780).

AI for Biomedical Applications

|

RET Site: Research Experiences for Teachers in Biologically-inspired Computing System

NSF CNS-1953544: Role: PI, Period: 3/2020-9/2024, Sponsor: National Science Foundation. |

As a key member at the Center of BioImaging and BioSystems, I have been collaborating with researchers in the College of Medicine and Mitchell Cancer Institute at the University of South Alabama on AI for biomedical applications. Specifically, my team has developed hyperspectral AI techniques for cancer detection, supported by the NSF grant CNS-1953544. Hyperspectral imaging (HSI) technologies present new opportunities to sample additional image and spectroscopic information from endoscopic procedures, and they offer tremendous potential for enhancing clinical cancer diagnostic instruments. However, HSI poses major challenges for data processing and classification algorithms due to the high dimensionality of the data. With the rapid development of AI techniques, deep learning has been widely used in the field of HSI classification. We have previously demonstrated AI-based analyses of HSI data based on Principal Component Analysis (PCA). Unfortunately, traditional HSI AI techniques cannot rapidly classify the volume of data to generate real-time results. Also, the “black-box” nature of AI techniques makes it difficult to interpret results for medical professionals. To overcome these limitations, in this project, my team has developed a scalable AI framework built for HSI image classification and interpretability, which (i) performs real-time HSI classification and automatically predicts whether a lesion is present or not as well as (ii) visualizes the exact location of the lesion if it is present. Read More on Project Website

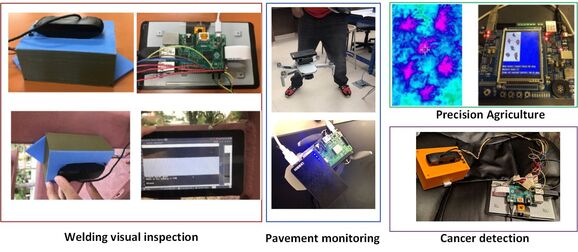

Embedded Vision: Bringing Machine Intelligence to Welding Visual Inspection, Pavement Monitoring, Agriculture, Cancer Detection, and Other Different Applications

Our team has also developed low-cost portable embedded vision device for different real-world applications such as welding visual inspection, pavement monitoring, and agriculture. With algorithm and hardware co-optimization, the developed devices can support advanced machine learning algorithms for real-time decision making.

Our Sponsors